Quartus Prime Lite Edition (無償)を使用して ROM IP をシミュレーションする方法を紹介します。

Intel の Quartus Prime 開発ソフトウェアのダウンロードから ライト・エディション(無償、ライセンス不要)をクリックして、下記の file をダウンロードします。

ダウンロードファイルの一例

サイズが大きい為、ダウンロードは時間がかかります。

QuartusLiteSetup-18.1.0.625-windows.exe を実行する。(ModelSim と Device file は自動でインストールされる)

Quartus Prime Lite Edition は、デフォルトで下記のディレクトリにインストールされます。

以上でインストールは終了です。次にプロジェクトを新規作成して ModelSim を呼び出す為の設定を行います。

新規プロジェクトを作成する前に、シミュレーションする VHDL を格納する為のディレクトリを作成します。ここでは C:\intelFPGA_lite の下に \ROM_1 を作成する。

Quartus Prime Lite を起動して、新規プロジェクトを作成します。

ここでは、Working Directory を C:\intelFPGA_lite\ROM_1、Project を ROM_1 と入力して NEXT をクリック

ここでは、Device : MAX10 DA の 10M08DAF256C7G を選択して、NEXT をクリック

以上でプロジェクトの作成は終了です。C:\intelFPGA_lite\ROM_1 に、2 つの file が作成される。

次に IP Catalog から 1 port ROM IP を取り出す。

IP Catalog の Library -> Basic Functions -> On Chip Memory -> ROM : 1-PORT をクリックする。

Save IP Variation で file name を C:/intelFPGA_lite/ROM_1/ROM_1、file type を VHDL にチェックして OK を押す。

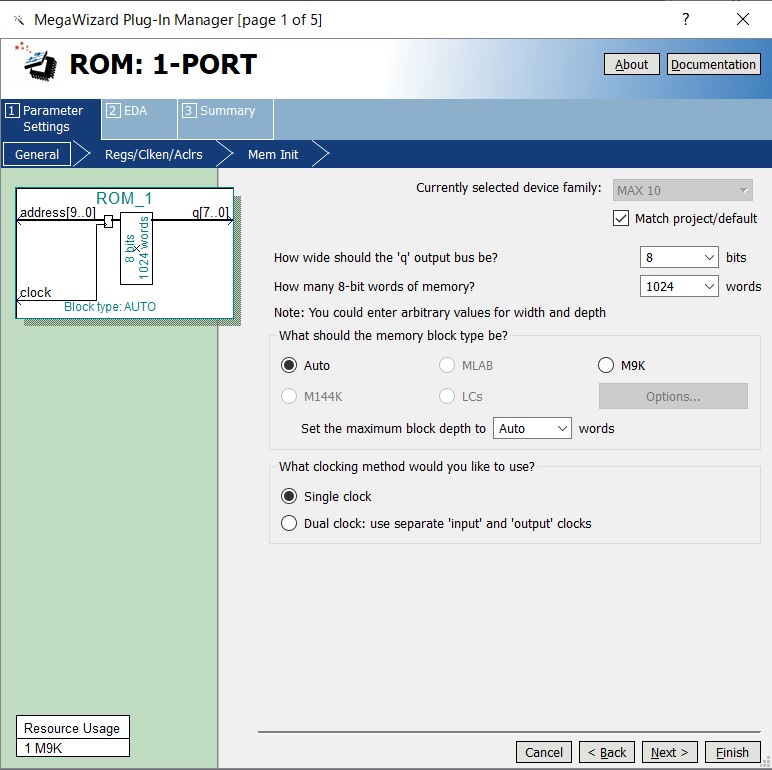

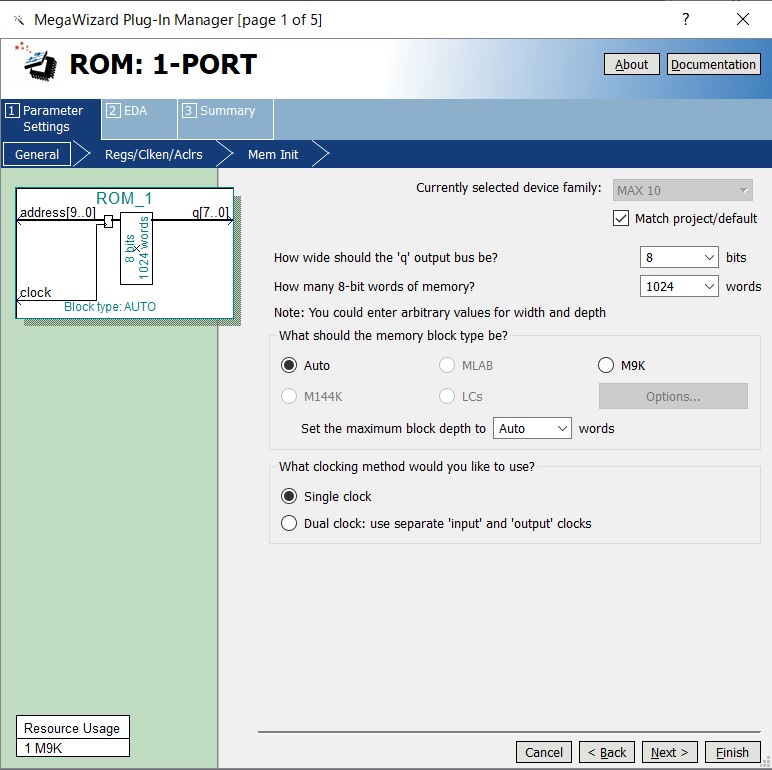

MegaWizard Plug-In Manager[Page 1 of 5] が開く。

ここでは、default のまま、Next を押す。

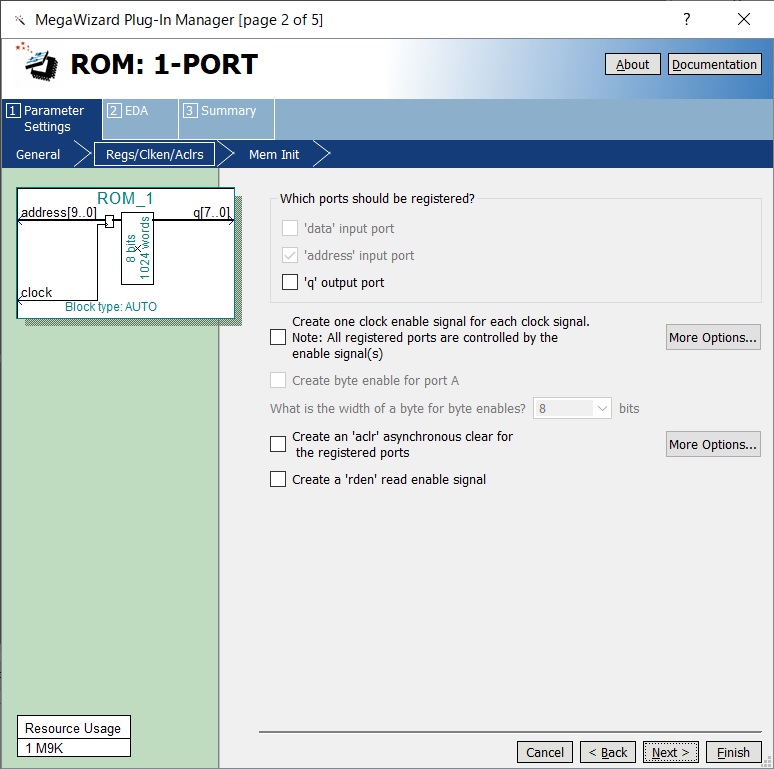

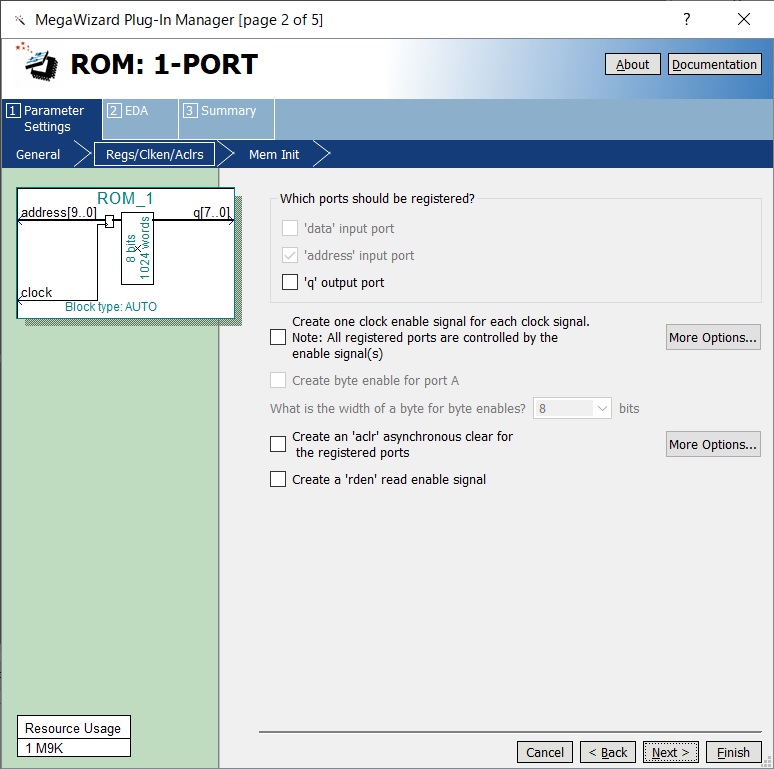

MegaWizard Plug-In Manager[Page 2 of 5] が開く。

ここでは、'q'output port のチェックを外して Next を押す。

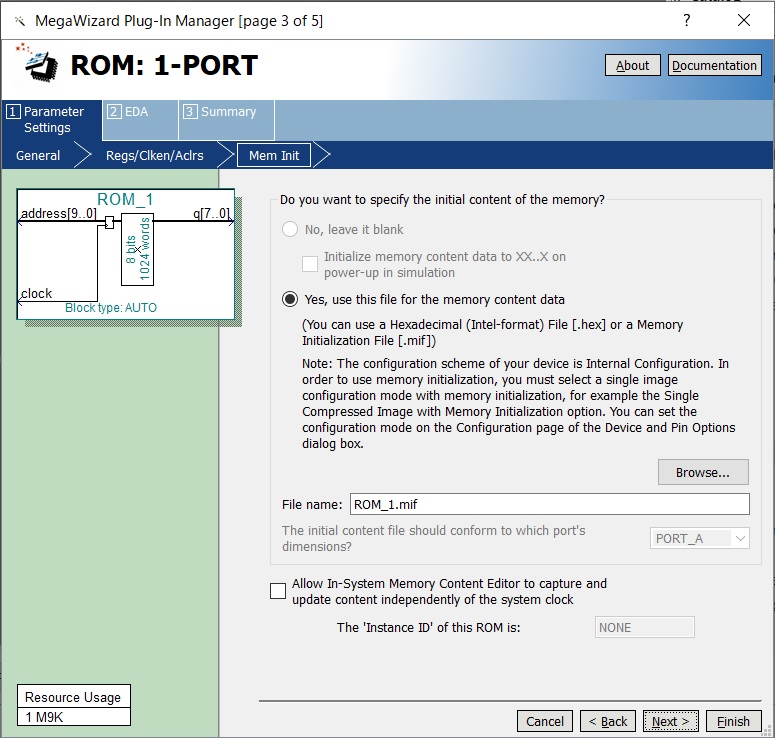

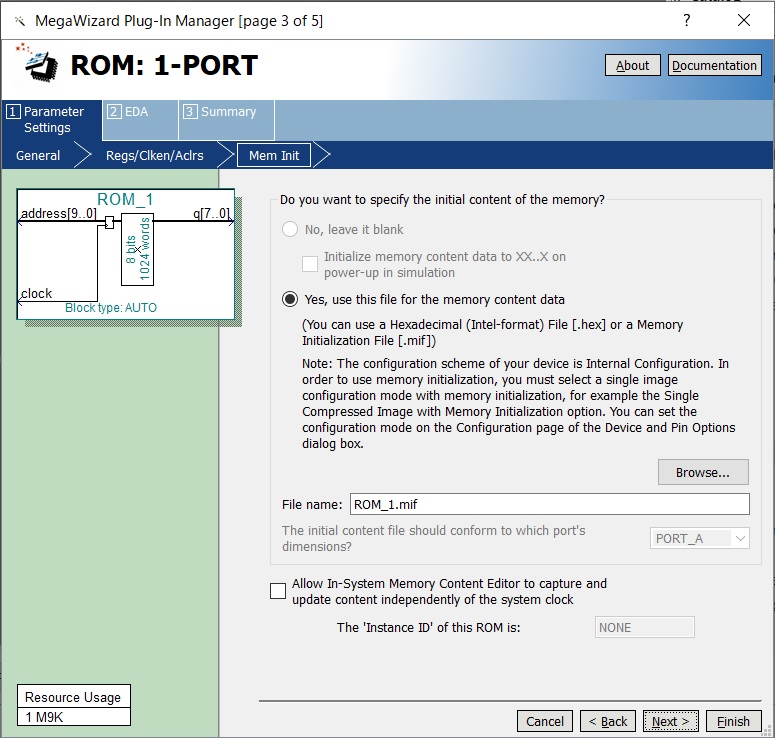

MegaWizard Plug-In Manager[Page 3 of 5] が開く。

ここでは、メモリデータの file name を C:/intelFPGA_lite/ROM_1/ROM_1.mif を選択して Next を押す。ROM_1.mif は別途作成しておく。

MegaWizard Plug-In Manager[Page 4 of 5] が開く。

ここでは、default のまま、Next を押す。

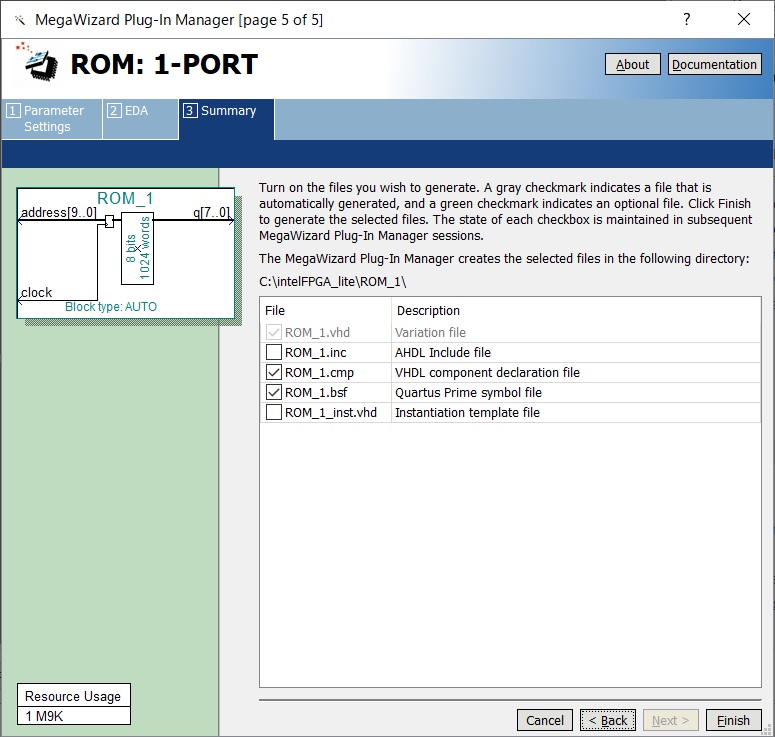

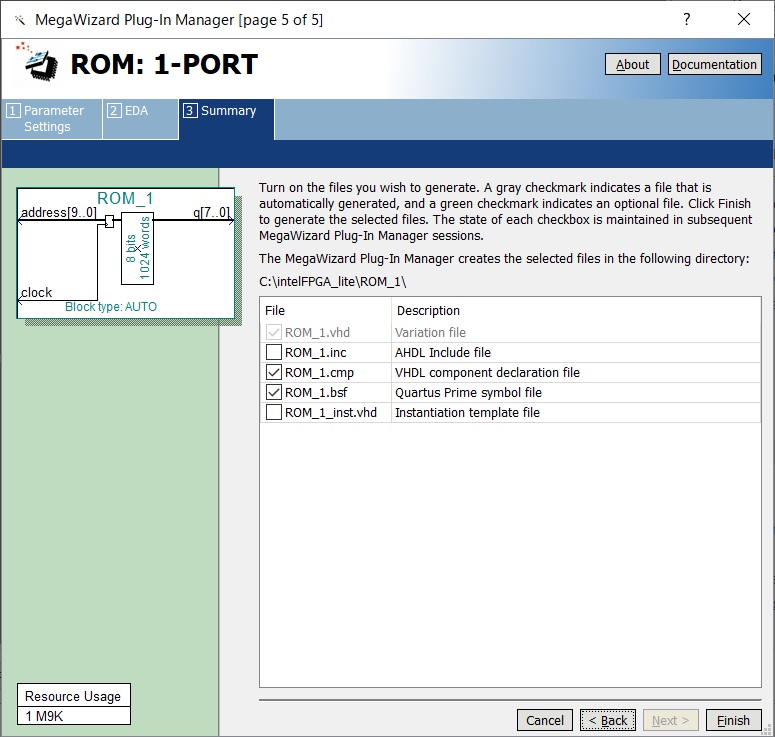

MegaWizard Plug-In Manager[Page 5 of 5] が開く。

ここでは、ROM_1.bsf をチェックして Finish を押す。

YES を押して終了する。

Project -> Add/Remeve Files In Project... を選択して、ROM_1.qip file が追加されていることを確認する。

次に On Chip Memory の初期化を有効にする。

Assignments -> Device -> Device and Pin Options -> Configuration -> Configuration mode で Single Compressed Image with Memory Initialization または Single Uncompressed Image with Memory Initialization を選択する。

シミュレーションを行うには、Design file の Analysis & Synthesis を実行して、error がないことが必要です。

次に、Analysis & Synthesis を実行します。

Task window -> Analysis & Synthesis をダブルクリック、成功すると、チェックマークが表示される。

error があると、error の箇所が表示されるので修正して、error がなくなるまで繰り返す。

ここまでできると、Analysis & Synthesis を再実行せずにシミュレーションを繰り返し実行することができます。

シミュレーションは、波形表示を設定しながら、繰り返し実行を行います。

次に、Quartus Prime Lite から ModelSim を呼び出す為の設定を行います。

下記を実行して、ModelSim が起動することを確認する。

ModelSim が起動すれば、呼び出しの設定は終了です。シミュレーションは、テストベンチ file がないので実行されない。ModelSim はクローズして終了する。

ここで、C:\intelFPGA_lite\ROM_1\simulation\modelsim directory が作成されていることを確認する。シミュレーションのテストベンチ file は、ここに置く。

次にテストベンチ file を作成して、シミュレーションを実行します。

テストベンチを下記のように設定する。

ここは、TB_TIMER.VHD を選択

ここでテストベンチ file : TB_ROM_1.VHD を追加

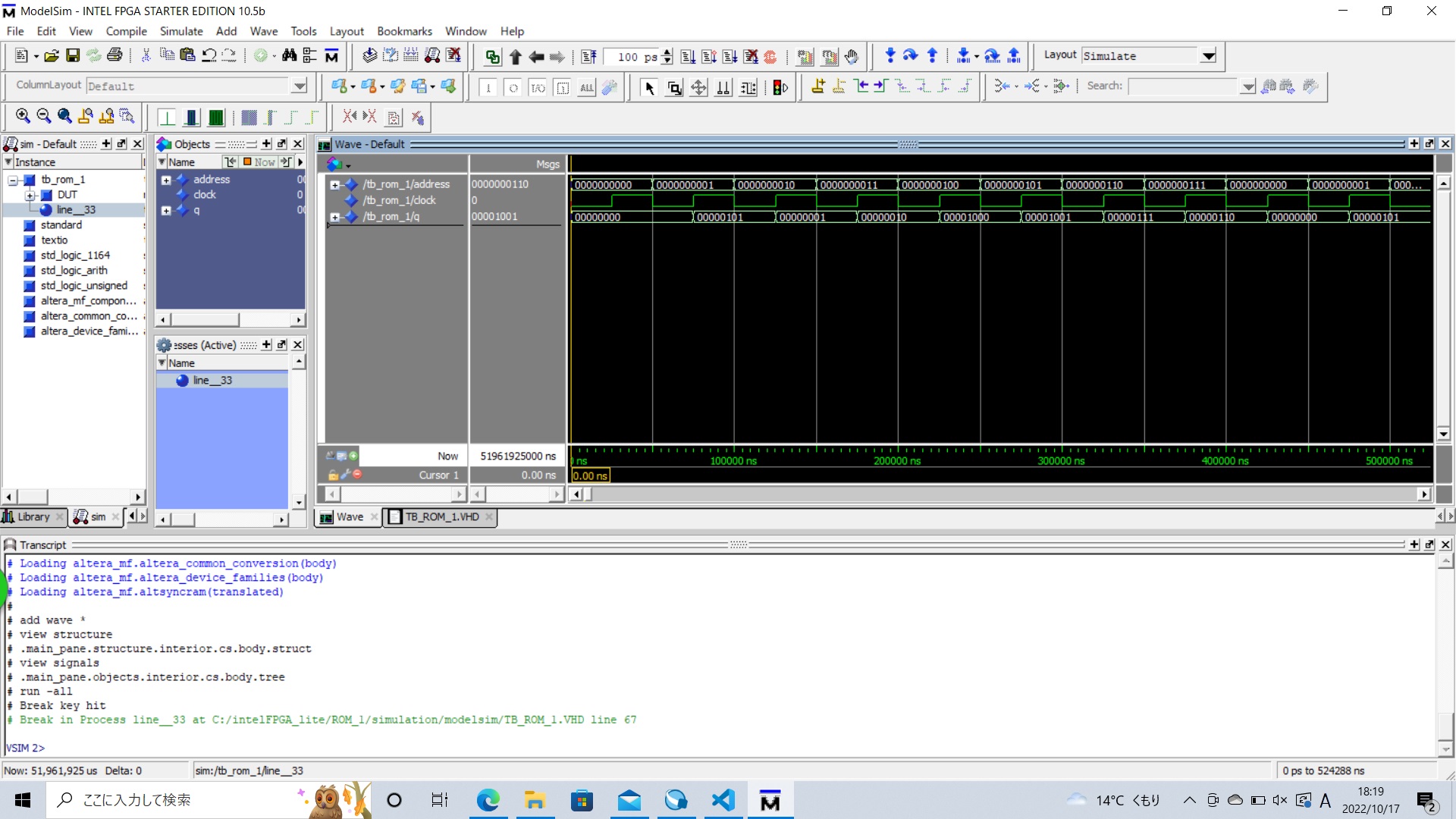

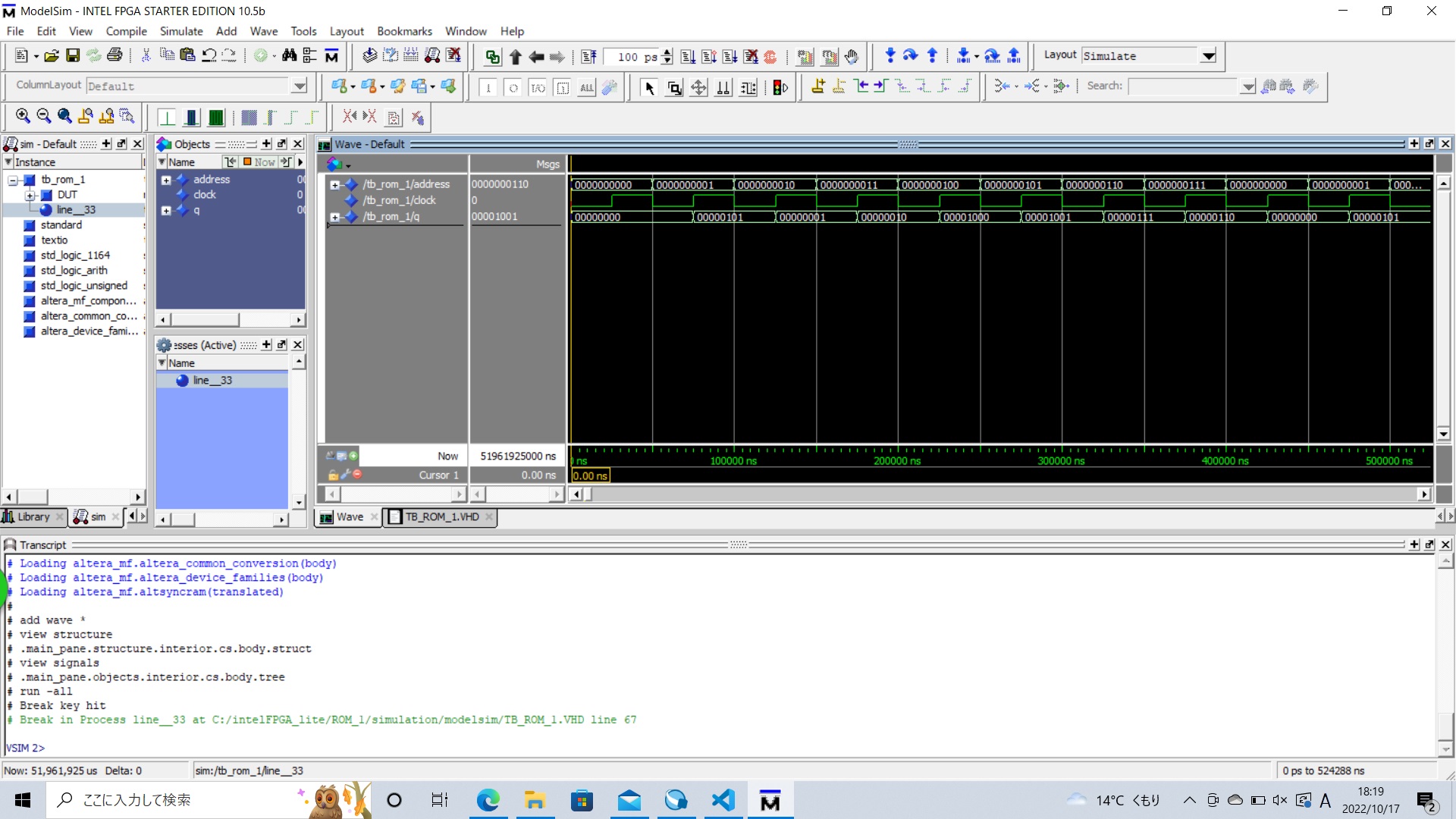

シミュレーションを実行する。

テストベンチに error がなければシミュレーションが開始する。シミュレーションは break するまで実行を続けているので、適当に Break して停止させる。

ModelSim の波形表示、保存、再実行 : 操作方法の簡単な説明です。

波形の拡大表示

波形の保存

波形の選択

シミュレーションの再実行

Wave 表示の保存

Wave の再表示