Quartus Prime Lite Edition を使用して VHDL をシミュレーションする

Quartus Prime Lite Edition (無償)を使用して VHDL をシミュレーションする方法を紹介します。

Intel の Quartus Prime 開発ソフトウェアのダウンロードから ライト・エディション(無償、ライセンス不要)をクリックして、下記の file をダウンロードします。

Quartus Prime Lite Edition Setup 実行 file

ModelSim Setup 実行 file

デバイス file : これがないと実行できない為、どれか一つを選択する。例えば、max10 を選択。

ダウンロードファイルの一例

QuartusLiteSetup-18.1.0.625-windows.exe : 1.7GByte

ModelSimSetup-18.1.0.625-windows.exe : 1.1GByte

max10-18.1.0.625.qdz : 339MByte

サイズが大きい為、ダウンロードは時間がかかります。

QuartusLiteSetup-18.1.0.625-windows.exe を実行する。(ModelSim と Device file は自動でインストールされる)

Quartus Prime Lite Edition は、デフォルトで下記のディレクトリにインストールされます。

C:\intelFPGA_lite

以上でインストールは終了です。次にプロジェクトを新規作成して ModelSim を呼び出す為の設定を行います。

新規プロジェクトを作成する前に、シミュレーションする VHDL を格納する為のディレクトリを作成します。ここでは C:\intelFPGA_lite の下に \test を作成する。

Quartus Prime Lite を起動して、新規プロジェクトを作成します。

Menu : File -> New Project Wizard

Introduction : NEXT をクリック

Directory,Name,Top-Level Entity : Working Directory、Name of project、Name of top-level design entity を入力。project と top-level design は同じにする。

ここでは、Working Directory を C:\intelFPGA_lite\test、Project を TIMER と入力して NEXT をクリック

Project Type : Empty project をチェックして1NEXT をクリック

Add Files : 灰色表示の "Add" の左横にある ",,,"をクリック、C:\intelFPGA_lite\test にある Design file をすべて選択して、"開く"をクリックする。

ここでは、TIMER.VHD を選択

Add Files : NEXT をクリック

Family,DEvice&Board Settings : Device を Available devices list の中から1つを選択。Filling を行わないの任意です。

ここでは、最下位行にある 10M50SCE144I7G を選択して、NEXT をクリック

EDA Tool Settings : Simulation の Tool Name : ModelSim-Altera、Format : VHDL を選択して、NEXT をクリック

Summary : Finish をクリック

以上でプロジェクトの作成は終了です。C:\intelFPGA_lite\test に、2 つの file が作成される。

TIMER.qpf

TIMER.qsf

シミュレーションを行うには、Design file の Analysis & Synthesis を実行して、error がないことが必要です。

次に、Analysis & Synthesis を実行します。

Task window -> Analysis & Synthesis をダブルクリック、成功すると、チェックマークが表示される。

error があると、error の箇所が表示されるので修正して、error がなくなるまで繰り返す。

ここまでできると、Analysis & Synthesis を再実行せずにシミュレーションを繰り返し実行することができます。

シミュレーションは、波形表示を設定しながら、繰り返し実行を行います。

次に、Quartus Prime Lite から ModelSim を呼び出す為の設定を行います。

Menu : Tools -> Options

General : EDA Tool Options の ModelSim-Altera の Directory を設定

C:\intelFPGA_lite\18.1\modelsim_ase\win32aloem\

下記を実行して、ModelSim が起動することを確認する。

Menu : Tools -> Run Simulation Tool -> RTL simulation

ModelSim が起動すれば、呼び出しの設定は終了です。シミュレーションは、テストベンチ file がないので実行されない。ModelSim はクローズして終了する。

ここで、C:\intelFPGA_lite\test\simulation\modelsim directory が作成されていることを確認する。シミュレーションのテストベンチ file は、ここに置く。

次にテストベンチ file を作成して、シミュレーションを実行します。

ここで、テストベンチ file : TB_TIMER.VHD とする。

テストベンチを下記のように設定する。

Menu : Assignments -> Settings

Category の EDA Tool Settings : Simulation の Native EDA Netlist Writer Settings の Compile test bench を選択、Test Benches をクリック

Existing test bench settings : New をクリック

Create new test bech settings の File name の欄に、Simulation のテストベンチ file を設定する。

ここは、TB_TIMER.VHD を選択

Existing test bench settings : Add をクリック

Test bench name : に TB_TIMER と入力する。(テストベンチの Top level Module)

Existing test bench settings : に TB_TIMER が追加される。

OK をクリック

Category の Files にテストベンチ file を追加する。

ここでテストベンチ file : TB_TIMER.VHD を追加

OK をクリック

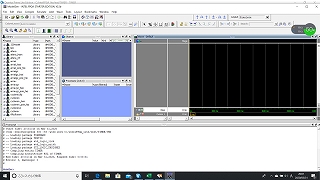

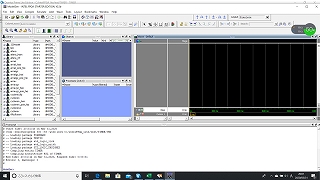

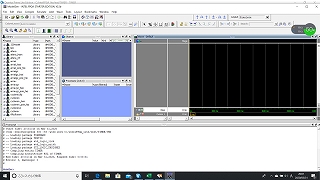

シミュレーションを実行する。

Menu : Tools -> Run Simulation Tool -> RTL simulation

テストベンチに error がなければシミュレーションが開始する。シミュレーションは break するまで実行を続けているので、適当に Break して停止させる。

ModelSim Menu : Simulate -> Break

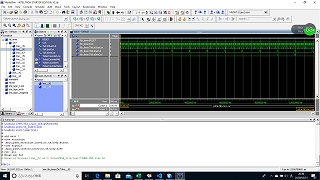

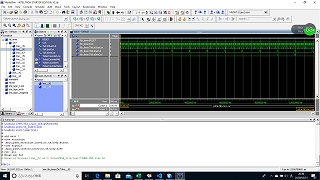

ModelSim の波形表示、保存、再実行 : 操作方法の簡単な説明です。

波形の拡大表示

Zoom In と Zoom Out で拡大、縮小

Select mode Icon を on (矢印マークの Icon)

Cursor1 or Cursor2 のどちらかを選択

表示エリアを Cursol1 と Cursol2 で設定

Zoom between cursols をクリック

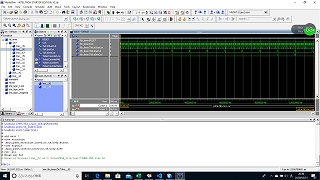

波形の保存

File -> Export -> Image

適当な Directory に保存する。Ex) C:\intelFPGA_lite\test\simulation\modelsim\bmp

波形の選択

Simulate -> Break で停止させた状態から、以下の操作で表示する波形を追加

Instance : 表示させたい波形が含まれている component を選択

Name : 信号の一覧から表示波形を選択、右クリック -> Add wave

source file を open、信号名を選択、右クリック -> Add wave

シミュレーションの再実行

Simulate -> Restart

Simulate -> Run -> Run-All

Wave 表示の保存

File -> Save Format

wave.do file : 波形表示する信号のリストが保存される。表示するにはシミュレーションを再実行する。

Wave の再表示

Transcript : do wave.do で wave.do file が読み込まれる。

wave.do file しか読み込まない為、wave.do を適当な名前に変更して保存しておく。再表示する時に、wave.do に変更して表示させる。

再表示するにはシミュレーションを再実行する。

2020-03-31

ホーム